via Ariosto, 35 • 44121 Ferrara urp@unife.it Tel. +39 0532 293111 www.unife.it

CONCORSO PUBBLICO, PER TITOLI ED ESAMI, PER LA COPERTURA DI N. 1 POSTO DI CATEGORIA D, POSIZIONE ECONOMICA D1, AREA TECNICA, TECNICO-SCIENTIFICA ED ELABORAZIONE DATI PER IL DIPARTIMENTO DI FISICA E SCIENZE DELLA TERRA PRESSO L'UNIVERSITÀ DI FERRARA

# CRITERI DI VALUTAZIONE DEI TITOLI E DELLE PROVE:

<u>Criteri per l'attribuzione dei punteggi per i titoli e l'esperienza documentata negli ambiti di</u> interesse del profilo:

Titoli di studio post-laurea e formazione documentata; fino ad un massimo di punti 10:

- Master di I livello fino a punti 1 sulla base della coerenza al bando.

- Laurea Magistrale, Laurea Vecchio Ordinamento, Laurea Magistrale a Ciclo Unico fino a punti 2 sulla base della coerenza al bando.

- Master di II livello fino a punti 1,5 sulla base della coerenza al bando

- Dottorato fino a punti 4, sulla base della coerenza al bando.

- Abilitazione alla professione o certificazione professionale fino a punti 0,5 sulla base della coerenza al bando.

- Corsi di Formazione fino a punti 0,25 con un limite massimo di 2 punti sulla base della coerenza al bando.

Esperienza documentata negli ambiti di interesse del profilo; fino ad un massimo di punti 20:

- 1 punto ogni 3 mesi per attività pienamente coerente col profilo

- 0,5 punti ogni 3 mesi per attività parzialmente coerente col profilo.

## Criteri e modalità di valutazione delle prove scritte:

- 1. Completezza della trattazione e sua attinenza alla traccia;

- 2. Livello di informazione documentata sulle tematiche proposte;

- 3. Chiarezza, correttezza e incisività nell'esposizione;

- 4. Elementi di originalità che dimostrano particolare competenza.

#### PROVE SCRITTE

### **PRIMA PROVA:**

# 1 - PROVA A:

Esercizio 1) In un tipico ambiente CAD professionale per la progettazione di schede elettroniche:

- quali proprieta' di un circuito stampato sono descritte dallo "stackup"?

- quali documenti necessari alla fabbricazione delle schede vengono in genere prodotti dagli strumenti di "Manufacturing Output"?

Esercizio 2) Durante la progettazione del layout di un circuito stampato si simula la trasmissione di un impulso di tensione nel circuito comprendente il pin di uscita di un circuito integrato trasmettitore, il pin di ingresso di un circuito integrato ricevitore e la traccia del circuito stampato che li collega. La traccia e il piano di massa sottostante si comportano come una linea di trasmissione con perdite trascurabili, impedenza caratteristica Z<sub>LINEA</sub> e ritardo di 50ns.

via Ariosto, 35 • 44121 Ferrara urp@unife.it Tel. +39 0532 293111 www.unife.it

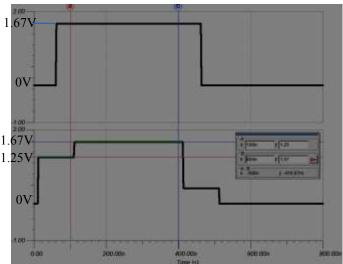

#### Sapendo che:

- lo stadio di uscita del trasmettitore si comporta come un generatore reale di tensione con impedenza-serie di uscita  $Z_{OUT}$  pari a  $100\Omega$  e con tensione a vuoto rappresentata da un impulso di durata 400ns ed ampiezza pari a 2.5V

- il ricevitore ha una impedenza di ingresso di  $100\Omega$

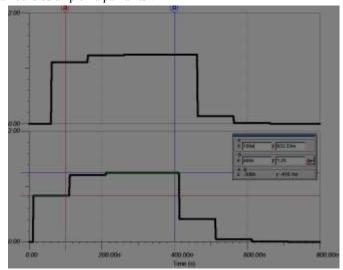

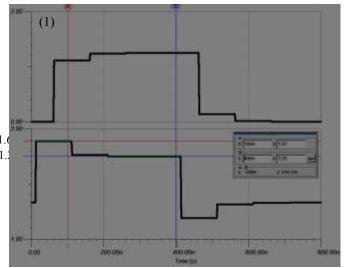

- il grafico (1) rappresenta la forma d'onda al pin di ingresso del ricevitore

- il grafico (2) rappresenta la forma d'onda al pin di uscita del trasmettitore

- l'ampiezza del segnale al pin di uscita del trasmettitore per i primi 100ns vale 833.33mV (cursore a)

- l'ampiezza del segnale al pin di uscita del trasmettitore vale 1.25V a 400ns, a transitorio approssimativamente esaurito (cursore b)

si dica se l'impedenza caratteristica  $Z_{\rm LINEA}$  della traccia e' adattata (cioe' se l'impedenza  $Z_{\rm LINEA}$  e' pari a  $100\Omega$ ) o si descriva, in caso contrario, come si interverebbe sui parametri della traccia o dello stackup del circuito stampato per raggiungere l'adattamento (cioe' la condizione  $Z_{\rm LINEA} = 100\Omega$ ).

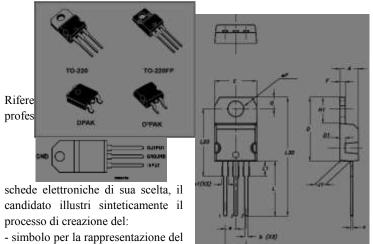

**Esercizio 3)** Il circuito integrato "three-terminal positive regulator" L7824CV e' disponibile, tra gli altri, nel package TO-220 i cui dettagli meccanici sono riportati nelle seguenti tavole:

| Clies.       |       |       |       |

|--------------|-------|-------|-------|

|              | Min   | Typ   | Max   |

| A            | 4.40  |       | 4.80  |

|              | 0.81  |       | 0.86  |

| 9.7          | 1.14  |       | 1.79  |

|              | 0.49  |       | 0.70  |

| D.           | 15.25 |       | 18.75 |

| THE STATE OF |       | 137   |       |

|              | 10    |       | 10.40 |

|              | 246   |       | 2.70  |

| at .         | 410   |       | 2.15  |

| F            | 1.23  |       | 1.32  |

| 907          | 6.29  |       | 8.60  |

| Jt           | 2.40  |       | 2.72  |

| L            | U     |       | 14    |

| 1.0          | 3.50  |       | 3,60  |

| 1.20         |       | 16.40 |       |

| L30          |       | 20.60 |       |

| SOF          | 3.75  | ļ.    | 3.85  |

| 10/          | 2.05  |       | 2.95  |

- simbolo per la rappresentazione del componente nello schema elettrico

- footprint per package TO-220 rappresentante il componente nel PCB layout

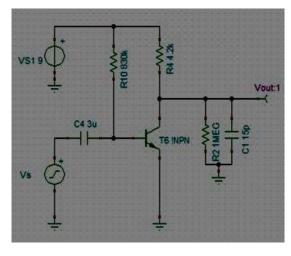

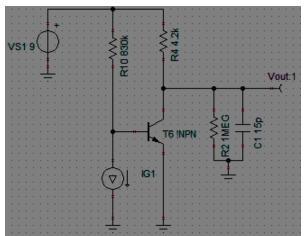

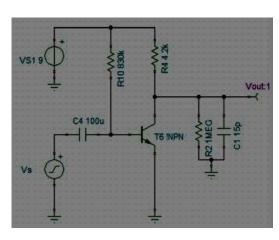

**Esercizio 4**) Dato il circuito rappresentato dallo schema elettrico a fianco dire quale tra i tool integrati in un tipico ambiente CAD per la progettazione elettronica si utilizzerebbe per ricavarne la risposta in frequenza del circuito  $G(\omega) = V_{out1}(\omega)/V_s(\omega)$ , descrivendo brevemente il tool ed il tipo di analisi che si dovrebbe effettuare.

Si stimi inoltre su quale intervallo di valori di pulsazione angolare  $\omega$  sia necessario condurre l'analisi per essere sicuri che vi si trovino compresi le pulsazioni di taglio inferiore e superiore della  $G(\omega)$ , sapendo che:

- Φ T6 ha un guadagno di corrente β = 100 ed e' polarizzato con una corrente di collettore a riposo di circa 1mA quindi l'impedenza dinamica di ingresso del transistor (connesso ad emettitore comune) e' pari approssimativamente a 2.5kΩ

- le capacita' parassite del transistor sono trascurabili

via Ariosto, 35 • 44121 Ferrara urp@unife.it Tel. +39 0532 293111 www.unife.it

#### Esercizio 5)

- Elencare ed esemplificare tipi di dati, standard e user-defined, rappresentabili in linguaggio VHDL

- Descrivere la differenza tra "blocking" e "non-blocking" assignments in linguaggio Verilog

Esercizio 6) Descrivere in VHDL o Verilog un sistema digitale "contatore" ad 8 bit con le seguenti caratteristiche:

- valore massimo del conteggio definito dalla costante MAXCOUNT (≤ 255) passata al modulo come "generic" in VHDL o come "parameter" in Verilog. Al raggiungimento del valore MAXCOUNT il conteggio deve ricominciare da 0

- o ingresso di clock

- ingresso di reset sincrono

- o ingresso di selezione del verso di conteggio

- uscita COUNT OUT ad 8 bit (di tipo std logic vector per descrizione VHDL)

**Esercizio 7)** In un tipico flusso di programmazione FPGA e' possibile lanciare simulazioni "RTL" (Register Transfer Level) oppure simulazioni "gate level". Descrivere sinteticamente le caratteristiche principali dell'uno e dell'altro tipo di simulazione.

#### Esercizio 8)

Utilizzando un linguaggio di programmazione di sua scelta il candidato scriva una funzione che riceva un numero intero N\_IN unsigned a 32bit (U32) e ritorni l'intero U32 N\_OUT corrispondente alla rappresentazione binaria di N\_IN modificata invertendo l'ordine dei bit

# 2 - PROVA B:

Esercizio 1) In un tipico ambiente CAD professionale per la progettazione di schede elettroniche:

- quali sono gli oggetti e le proprieta' degli stessi che vengono verificati dal tool per "Design Rule Check" elettrico (per alcuni CAD si parla in questo caso di Electrical Rule Check)?

- con riferimento al layout del circuito stampato per una scheda elettronica quali sono gli oggetti e le proprieta' degli stessi che vengono verificati dal tool per "Design Rule Check"?

- in quali fasi della progettazione di un circuito stampato vengono utilizzate le proprieta' descritte dallo "stackup"?

Esercizio 2) Durante la progettazione del layout di un circuito stampato si simula la trasmissione di un impulso di tensione nel circuito comprendente il pin di uscita di un circuito integrato trasmettitore, il pin di ingresso di un circuito integrato ricevitore e la traccia del circuito stampato che li collega. La traccia e il piano di massa sottostante si comportano come una linea di trasmissione con perdite trascurabili, impedenza caratteristica Z<sub>LINEA</sub> e ritardo di 50ns.

Sapendo che:

- lo stadio di uscita del trasmettitore si comporta come un generatore reale di tensione con impedenza-serie di uscita Zout pari a

- $100\Omega$  e con tensione a vuoto rappresentata da un impulso di durata 400ns ed ampiezza pari a 2.5V

- il ricevitore ha una impedenza di ingresso di  $100\Omega$

- il grafico (1) rappresenta la forma d'onda al pin di ingresso del ricevitore

- il grafico (2) rappresenta la forma d'onda al pin di uscita del trasmettitore

- l'ampiezza del segnale al pin di uscita del trasmettitore per i primi 100ns vale 1.67V (cursore a)

- l'ampiezza del segnale al pin di uscita del trasmettitore vale 1.25V a 400ns, a transitorio approssimativamente esaurito (cursore b)

- si dica se l'impedenza caratteristica  $Z_{\rm LINEA}$  della traccia e' adattata (cioe' se l'impedenza  $Z_{\rm LINEA}$  e' pari a  $100\Omega$ ) o si descriva, in caso contrario, come si interverebbe sui parametri della traccia o dello stackup del circuito stampato per raggiungere l'adattamento (cioe' la condizione  $Z_{\rm LINEA}$  =  $100\Omega$ ).

via Ariosto, 35 • 44121 Ferrara urp@unife.it Tel. +39 0532 293111 www.unife.it

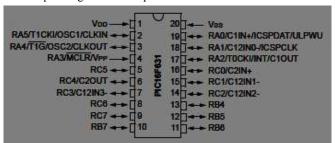

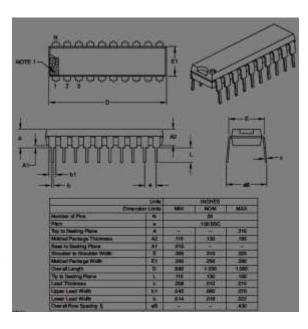

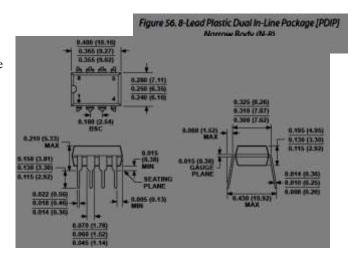

**Esercizio 3)** Il data sheet del circuito integrato PIC16F690-I/P lo descrive come "20-Pin Flash-Based, 8-Bit CMOS Microcontrollers", disponibile nel package 20-Lead PDIP (Plastic Dual In-line) i cui dettagli dimensionali sono riportati nelle tavole a fianco. La tavola sotto illustra invece il pin-diagram del componente

Riferendosi ad un ambiente CAD professionale per la progettazione di schede elettroniche di sua scelta, il candidato illustri sinteticamente il processo di creazione del:

- simbolo per la rappresentazione del componente nello schema elettrico

- footprint rappresentante il componente nel PCB layout

Esercizio 4) Dato lo schema elettrico a fianco dire quale tra i tool integrati in un tipico ambiente CAD per la progettazione elettronica si utilizzerebbe per stimare l'andamento temporale della risposta in uscita  $V_{out1}(t)$  del circuito, inizialmente in quiete, al segnale fornito dal generatore ideale  $I_{G1}$  e rappresentato da un gradino di corrente  $I_{G1}(t)$  di intensità'  $I_{G1}(t)$  di intensit

Si descriva brevemente il tool scelto, il tipo di analisi da effettuare e si stimi su quale intervallo temporale sia necessario condurre l'analisi perche' si possa considerare raggiunto il nuovo stato di equilibrio dopo l'applicazione di  $I_{\rm GI}(t)$ , sapendo che:

- $\mathbf{Φ}$  T6 ha un guadagno di corrente  $\beta = 100$  ed e' polarizzato con una corrente di collettore a riposo di circa 1mA quindi l'impedenza dinamica di ingresso del transistor connesso ad emettitore comune e' pari approssimativamente a  $2.5 \mathrm{k}\Omega$

- le capacita' parassite del transistor sono trascurabili

#### Esercizio 5)

- Descrivere la differenza tra un oggetto VHDL di tipo "variable" ed uno di tipo "signal"

- Dato il seguente segmento di codice Verilog in cui sono utilizzate assegnazioni "non-blocking" ( <= ) dire dopo quanti periodi del clock "i\_clock" l'oggetto "r\_test\_3" assume il valore 1'b1:

```

reg r_Test_1 = 1'b0;

reg r_Test_2 = 1'b0;

reg r_Test_3 = 1'b0;

always @(posedge i_clock)

begin

r_Test_1 <= 1'b1;

r_Test_2 <= r_Test_1;

r_Test_3 <= r_Test_2;

end

```

Esercizio 6) Descrivere in VHDL o Verilog un sistema digitale "contatore" ad N bit con le seguenti caratteristiche:

• numero di bit definito dalla costante N passata al modulo come "generic" in VHDL o come "parameter" in Verilog. il conteggio deve arrivare al valore 2<sup>N</sup>-1 e poi ricominciare da 0

via Ariosto, 35 • 44121 Ferrara urp@unife.it Tel. +39 0532 293111 www.unife.it

- ingresso di clock

- ingresso di reset asincrono e sincrono

- ingresso di abilitazione del conteggio

- uscita di dimensione N (di tipo std logic vector per descrizione VHDL)

Esercizio 7) In un tipico flusso di programmazione FPGA la funzionalita' del progetto puo' essere riscontrata mediante simulazioni "RTL" (Register Transfer Level) e verifiche dei risultati dell'invocazione del tool di "Static Timing Analysis". Descrivere sinteticamente le caratteristiche principali dell'uno e dell'altro tipo di analisi.

#### Esercizio 8)

Utilizzando un linguaggio di programmazione di sua scelta il candidato scriva una funzione che riceva un numero intero N\_IN unsigned a 32bit (U32) e ritorni l'intero U32 N\_OUT corrispondente alla rappresentazione binaria di N\_IN modificata scambiando tra loro il gruppo da 16 bit di ordine meno significativo della rappresentazione binaria con il gruppo da 16bit di ordine piu' significativo

# 3 - PROVA C:

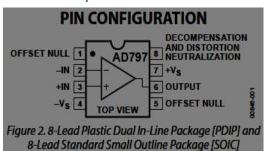

**Esercizio 1)** Il circuito integrato AD797ANZ e' un "very low noise, low distortion operational amplifier" con il pin diagram riportato sotto e i dettagli costruttivi del package "8-Lead PDIP" riportati nella tavola a fianco:

Riferendosi ad un ambiente CAD professionale per la progettazione di schede elettroniche di sua scelta, il candidato illustri sinteticamente il processo di creazione del:

- simbolo per la rappresentazione del componente nello schema elettrico

- footprint rappresentante il componente nel PCB layout

Esercizio 2) In un tipico ambiente CAD professionale per la progettazione di schede elettroniche:

- quali specifici tool software necessitano delle informazioni relative allo "stackup"?

- quale corredo di documentazione necessaria per la fabbricazione del circuito stampato e il montaggio della scheda e' generalmente prodotta dall'ambiente CAD?

### Esercizio 3)

Dato lo schema elettrico a fianco dire quale tra i tool integrati in un tipico ambiente CAD per la progettazione elettronica si utilizzerebbe per ricavare l'andamento temporale della risposta in uscita  $V_{\text{out}1}(t)$  del circuito, inizialmente in quiete, al segnale in ingresso  $V_s(t)$ , rappresentato da una sinusoide con ampiezza di picco pari a 10mV e frequenza pari a 10kHz (compresa nella banda passante del circuito).

Si descriva brevemente il tool scelto, il tipo di analisi da effettuare e si stimino valore medio e ampiezza del segnale di uscita sapendo che:

via Ariosto, 35 • 44121 Ferrara urp@unife.it Tel. +39 0532 293111 www.unife.it

- T6 ha un guadagno di corrente  $\beta = 100$  ed e' polarizzato con una corrente di collettore a riposo di circa 1mA quindi l'impedenza dinamica di ingresso del transistor in regime lineare e' pari approssimativamente a  $2.5k\Omega$

- le capacita' parassite del transistor sono trascurabili

Esercizio 4) Durante la progettazione del layout di un circuito stampato si simula la trasmissione di un impulso di tensione nel circuito comprendente il pin di uscita di un circuito integrato trasmettitore, il pin di ingresso di un circuito integrato ricevitore e la traccia del circuito stampato che li collega. La traccia e il piano di massa sottostante si comportano come una linea di trasmissione con perdite trascurabili, impedenza caratteristica Z<sub>LINEA</sub> e ritardo di 50ns.

Sapendo che:

- lo stadio di uscita del trasmettitore si comporta come un generatore reale di tensione con impedenza-serie di uscita  $Z_{OUT}$  pari a  $50\Omega$  e con tensione a vuoto rappresentata da un impulso di durata 400ns ed ampiezza pari a 2.5V

- l' impedenza caratteristica della linea  $\, Z_{LINEA} \,$  e' stimata dal simulatore in  $\, 50\Omega , \,$  sulla base dei parametri costruttivi del circuito

- il grafico (1) rappresenta la forma d'onda al pin di ingresso del ricevitore

- il grafico (2) rappresenta la forma d'onda al pin di uscita del 1.25V trasmettitore

- l'ampiezza del segnale al pin di uscita del trasmettitore per i primi 100ns vale 1.25V (cursore a)

- l'ampiezza del segnale al pin di uscita del trasmettitore vale 1.67V a 400ns, a transitorio approssimativamente esaurito (cursore b)

si dica, analizzando le forme d'onda qui riportate, se per il

circuito costituito da trasmettitore, traccia e ricevitore con impedenza di ingresso  $Z_{\text{IN\_RICEVITORE}}$  sia verificata la condizione di adattamento:  $Z_{\text{OUT}} = Z_{\text{LINEA}} = Z_{\text{IN\_RICEVITORE}}$ . Stimare, in caso contrario, il valore dell'impedenza di ingresso  $Z_{\text{IN\_RICEVITORE}}$ .

**Esercizio 5)** Utilizzando un linguaggio di programmazione di sua scelta il candidato scriva una funzione che riceva un numero intero N\_IN unsigned a 32bit (U32) e ritorni l'intero U32 N\_OUT corrispondente alla rappresentazione binaria di N\_IN modificata scambiando tra loro il gruppo da 8 bit di ordine meno significativo della rappresentazione binaria con il gruppo da 8 bit di ordine piu' significativo

### Esercizio 6)

- Elencare ed esemplificare sinteticamente tipi e sottotipi di dati rappresentabili in linguaggio VHDL

- Dato il seguente segmento di codice Verilog in cui sono utilizzate assegnazioni "blocking" (=) dire dopo quanti periodi del clock "i\_clock" l'oggetto "r\_test\_3" assume il valore 1'b1:

```

reg r_Test_1 = 1'b0;

reg r_Test_2 = 1'b0;

reg r_Test_3 = 1'b0;

always @(posedge i_clock)

begin

r_Test_1 = 1'b1;

r_Test_2 = r_Test_1;

r_Test_3 = r_Test_2;

end

```

Esercizio 7) Descrivere in VHDL o Verilog un sistema digitale "shift register" con le seguenti caratteristiche:

- numero di bit del registro definito dalla costante NUM\_REG passata al modulo come "generic" in VHDL o come "parameter" in Verilog.

- o ingresso di clock

- ingresso di reset sincrono

- ingresso seriale D\_IN (di tipo std\_logic per la descrizione VHDL)

- uscita parallela di dimensione NUM\_REG di tipo std\_logic\_vector (solo per descrizione VHDL)

Università degli Studi di Ferrara via Ariosto, 35 • 44121 Ferrara urp@unife.it Tel. +39 0532 293111

Tel. +39 0532 29 www.unife.it

Esercizio 8) Elencare e descrivere sinteticamente i tool integrati in un tipico ambiente di progammazione FPGA utilizzabili dal progettista per la verifica sintattica e per la verifica funzionale della descrizione comportamentale fornita dai sorgenti scritti nell' "Hardware Description Language" scelto (es. Verilog, VHDL, etc.).

# **SECONDA PROVA:**

### 1 - PROVA A:

**Tema 1)** Il candidato illustri, con riferimento ad un ambiente CAD professionale per progettazione elettronica di sua scelta, il flusso di sviluppo di una scheda elettronica che porta alla preparazione della tipica documentazione di output del CAD (es. lista componenti, file GERBER etc.) necessaria alla fabbricazione del circuito stampato della scheda e al montaggio dei componenti. Si supponga di partire da uno schema elettrico completo realizzato mediante l'apposito tool integrato nell'ambiente stesso.

**Tema 2)** Si elenchino e si descrivano brevemente, con riferimento ad un ambiente di sviluppo per FPGA scelto dal candidato, i tools dell'ambiente che vengono impiegati per ottenere, a partire dai sorgenti in Hardware Description Language, il file oggetto da trasferire alla memoria SRAM (volatile) di configurazione del dispositivo FPGA di destinazione ("target FPGA"). Si descriva almeno uno dei possibili metodi impiegati in genere per la configurazione, al power-up, del target FPGA da un dispositivo di memoria non volatile esterno.

Tema 3) Un oscilloscopio digitale e' dotato di una porta seriale, di una porta USB e di una porta LAN-Ethernet. Attraverso la porta attiva, quella scelta dal candidato tra le tre disponibili, lo strumento (o meglio il suo processore interno) puo' ricevere e processare comandi SCPI ("Standard Commands for Programmable Instruments") consistenti in stringhe di caratteri ASCII terminate da un carattere new line "\n". Un esempio e' la query "\*IDN?\n" che richiede l'identificativo dello strumento, a cui l'oscilloscopio risponde con la stringa "Teledyne Test Tools, T3DSO1204, NDS1EBAC0L0098,7.6.1.15". Utilizzando un linguaggio/ambiente di programmazione a sua scelta il candidato scriva un programma da eseguire su un PC connesso all'oscilloscopio che, una volta lanciato dall'utente, apra il canale di comunicazione, invii il comando "\*IDN?\n" all'oscilloscopio, riceva e visualizzi la risposta e quindi chiuda il canale di comunicazione. Il candidato illustri brevemente le motivazioni della scelta di linguaggio/ambiente di programmazione.

# 2 - PROVA B:

**Tema 1)** Il candidato illustri, con riferimento ad un ambiente CAD professionale per progettazione elettronica di sua scelta, un esempio di applicazione dei tool di controllo delle regole di progetto elettrico e di layout e un esempio di applicazione di tool di signal integrity analysis.

**Tema 2)** Il candidato elenchi e descriva brevemente, con riferimento ad un ambiente di sviluppo per FPGA di sua scelta, i tool che permettono al progettista di:

- o editare e verificare dal punto di vista sintattico e funzionale i file sorgenti in linguaggio VHDL e/o Verilog

- ° ottenere dai file sorgenti il file di configurazione per il dispositivo FPGA di destinazione ("target FPGA")

- o trasferire il file di configurazione al target FPGA e verificare "in-vivo" la funzionalita' del target FPGA mediante cattura e rappresentazione dello stato o dell'evoluzione di segnali interni

- $\circ$ garantire che il progetto installato nel target FPGA rispetti le specifiche temporali ("timing closure").

**Tema 3)** Il tool di simulazione di un ambiente di sviluppo per FPGA legge da un file di testo "input.txt" una serie di 100 numeri unsigned a 32 bit (U32) rappresentati in formato esadecimale (es. 0X1A2B3C4D) da trasmettere, durante una sessione di simulazione, ad un modulo VHDL "ordinatore.vhd", la funzione del quale e' quella di memorizzare i dati entranti in un buffer di ingresso, eleborarli e salvarli in un buffer di uscita riordinati per valore crescente. Al termine della sessione di simulazione viene creato il file di testo "ordered.txt" che contiene, rappresentati in formato esadecimale, i 100 numeri U32 riordinati.

Utilizzando un linguaggio/ambiente di programmazione a sua scelta il candidato scriva un programma che prepari il file "input.txt" con i 100 numeri U32 di cui sopra, generandoli in modo che abbiano valori casuali ma senza ripetizioni e quindi un programma che verifichi che nel file "ordered.txt" prodotto dal simulatore siano presenti tutti i 100 numeri correttamente ordinati in senso crescente stampando un avviso a schermo in caso contrario. Il candidato illustri brevemente le motivazioni della scelta di linguaggio/ambiente di programmazione.

Università degli Studi di Ferrara via Ariosto, 35 • 44121 Ferrara urp@unife.it Tel. +39 0532 293111 www.unife.it

### 3- PROVA C:

**Tema 1)** Il candidato elenchi e descriva brevemente i tool forniti da un ambiente CAD professionale di sua scelta per supportare tutte le fasi di progettazione di una scheda elettronica che vanno dalla creazione dello schema elettrico, al layout, alla produzione della documentazione necessaria alla fabbricazione della scheda (es. lista componenti, file GERBER etc.).

Tema 2) Si elenchino e si descrivano brevemente, con riferimento ad un ambiente di sviluppo per FPGA scelto dal candidato, i tools dell'ambiente che vengono impiegati per ottenere, a partire dai sorgenti in Hardware Description Language, il file oggetto da trasferire alla memoria SRAM (volatile) di configurazione del dispositivo FPGA di destinazione ("target FPGA"). Si descriva in particolare il tool di Static Timing Analysis e il suo ruolo nel garantire che il progetto installato nel target FPGA rispetti le specifiche temporali ("timing closure").

Tema 3) Un oscilloscopio digitale e' dotato di una porta seriale, di una porta USB e di una porta LAN-Ethernet. Attraverso la porta attiva, quella scelta dal candidato tra le tre disponibili, lo strumento (o meglio il suo processore interno) puo' ricevere e processare comandi SCPI ("Standard Commands for Programmable Instruments") consistenti in stringhe di caratteri ASCII terminate da un carattere new line "\n". Un esempio e' la query "C1:VDIV?\n" che richiede l'impostazione di sensibilita' verticale del canale 1, a cui l'oscilloscopio risponde con la stringa "C1:VDIV 5.00E-01V". Utilizzando un linguaggio/ambiente di programmazione a sua scelta il candidato scriva un progamma da eseguire su un PC connesso all'oscilloscopio che, una volta lanciato dall'utente, apra il canale di comunicazione, invii il comando "C1:VDIV?\n" all'oscilloscopio, riceva e visualizzi la risposta e quindi chiuda il canale di comunicazione. Il candidato illustri brevemente le motivazioni della scelta di linguaggio/ambiente di programmazione.

Ferrara, 16 luglio 2020

IL PRESIDENTE DELLA COMMISSIONE Prof.ssa Eleonora LUPPI

Elenne lux